# proceedings of the 2 ystems imulation

February 12-14

Faculty of Electronic Engineering

Niš, Serbia

organized by

#### **Publisher:**

Faculty of Electronic Engineering, University of Niš Aleksandra Medvedeva 14, 18000 Niš http://elfak.ni.ac.rs

and

Innovation Centre of Advanced Technologies Bulevar Nikole Tesle 61, lokal 5 18000 Niš http://www.icnt.rs

#### **Editor:**

Predrag Petković

СІР - Каталогизација у публикацији - Народна библиотека Србије, Београд

519.876.5(082) 004.942(082)

SMALL Systems Simulation Symposium (6th; 2016; Niš) Proceedings of the Small Systems Simulation Symposium 2016, 6 th, February 12-14, Niš, Serbia / organized by Innovation Centre of Advanced Technologies and Faculty of Electronic Engeneering, Niš; [editor Predrag Petković]. - Niš: Faculty of Electronic Engineering: Innovation Centre of Advanced Technologies, 2016 (Niš: Unigraf). - 147 str.: ilustr.; 30 cm

Tekst štampan dvostubačno. - Tiraž 70. - Bibliografija uz svaki rad. - Registar.

ISBN 978-86-6125-154-2 (FEE)

- 1. Innovation Centre of Advanced Technologies (Niš)

- а) Симулација Зборници

COBISS.SR-ID 221247756

Dear colleagues, dear friends, dear guests,

The 6<sup>th</sup> SSSS Conference is continuing the tradition established in the year 2000 when the First Small Systems Simulation Symposium took place, here, in the city of Niš at the Faculty of Electronic Engineering of the University of Niš. And now after 16 years one could ask what the frequency of our gathering is? How it happened that in 16 years we have six meetings? The "secret" is very simple. First three Symposia were occurred with time step of five years. Then after 2010, on the request of scientific community, we decided to meet more often - each two years.

The idea about gathering to "promote our research results and especially the results of our young associates in an environment and atmosphere that was supposed to be correctly critical and, in the same time, encouraging enough for further endeavours" come from Prof. Vančo Litovski. He has established SSSS and I want to express my gratitude for this heritage. At the beginning it was not easy to attract scientists from abroad to participate to a new Symposium. However Prof. Litovski has asked his friends from the University of Southampton, Middlesex University, University from Besancon, Technical University of Vienna, Deft University, and others to send papers and SSSS2000 was born as an international meeting. Later on, support from Balkan countries was priceless, as well. Our colleagues from Belgrade, Banja Luka, Sarajevo, Novi Sad, Skopje, and Sofia become our regular participants. This has helped to rebuild some old connection and to establish some new. Moreover, we had participants from Spain, Germany, Armenia, and Australia. In a friendly atmosphere new ideas have emerged so that SSSS participants have appeared as consortia in few European projects.

This friendship was established on professional respect and consequently it lasts ever since. We are gathered again to present results of our bi-annual efforts not just to promote our achievements but also to introduce the young associates in this community.

The keyword of SSSS points to simulation. Simulations appear here in all their shapes and forms: starting from modelling and simulation algorithms ending as a tool for design verification.

This year we have papers categorized in two sessions dedicated to modelling and two to simulations. We cover everything from modelling arks and 3D Tesla's generator/motor, over modelling effects in FinFETs, telecommunication and information networks, to the modelling electrical vehicles. In simulation area there will be papers about simulators, new implemented simulation methods, and simulation results on system and circuit level.

Special plenary session will be dedicated to the bottle-neck of our scholar system – cooperation between academia and SMEs. We are going to see presentations from Professor Simon La Blond from the University of Bath, the leading UK university with an international reputation for teaching and research excellence, and the Rector of the Metropolitan University from Belgrade, Professor Dragan Domazet about their experiences in this area.

This Symposium would not happen without broad support from Faculty of Electronic Engineering, all members of LEDA laboratory and especially Dr Marko Dimitrijević, as well as from the Innovation Centre of Advanced Technologies, from Niš and particularly Dr Jelena Milojković.

Respectfully Prof. Predrag Petković

The 6<sup>th</sup> Small Systems Simulation Symposium

was supported by

Ministry of Education, Science, and Technological Development of Serbia,

LMB Soft d.o.o. Niš, Serbia

Iritel a.d. Beograd, Serbia

Irvas International d.o.o. Niš, Serbia

Bel Systems d.o.o. Beograd, Serbia

#### STEERING COMMITTEE

- S. Bojanić, Universidad politécnica de Madrid (Spain)

- B. Blagojević, University of Niš, Serbia

- **I. Bushehri**, Lime Microsystems, (United Kingdom)

- B. Damper, University of Southampton

- **B. Dokić**, University of Banja Luka (Bosnia and Herzegovina)

- G. S. Djordjević, University of Niš (Serbia)

- N. Janković, University of Niš (Serbia)

- M. Jevtić, University of Niš (Serbia)

- T. Kazmierski, University of Southampton

- V. Litovski, University of Bath (United Kingdom)

- V. Melikyan, Director of Educational Department, Synopsys Armenia CJSC

- S. Milenković, Lime microsystems (United Kingdom)

- O. Nieto, Universidad politécnica de Madrid (Spain)

- D. Pantić, University Niš (Serbia)

- P. Petković, University of Niš (Serbia)

- B. Reljin, University of Belgrade (Serbia)

- M. Smiljanić, Academy of Engineering Sciences (Serbia)

- S. Stanković, University of Belgrade (Serbia)

- **D. Trajanov**, FCSE (FINKI) Skopje (Macedonia)

- V. Zerbe, Technical University of Erfurt (Germany)

- M. Živanov, University of Novi Sad (Serbia)

- M. Zwolinski, University of Southampton (United Kingdom)

#### **ORGANIZING COMMITEE**

- M. Andrejević Stošović, University of Niš (Serbia)

- S. Bojanić, Universidad Politecnica de Madrid (Spain)

- M. Dimitrijević, University of Niš (Serbia)

- S. Đorđević, University of Niš (Serbia)

- B. Jovanović, University of Niš (Serbia)

- V. Litovski, University of Bath (United Kingdom)

- M. Milić, University of Niš (Serbia)

- J. Milojković, ICAT (Serbia)

- D. Milovanović, University of Niš (Serbia)

- **D. Mirković**, University of Niš (Serbia)

- P. Petković, University of Niš (Serbia)

- **Z. Petković**, University of Niš (Serbia)

## **Symposium Secretary**

#### Marko Dimitrijević

Faculty of Electronic Engineering

University of Niš

Aleksandra Medvedeva 14

18000 Niš

Serbia

Tel: +381 18 529321

marko@venus.elfak.ni.ac.rs

# **Proceedings of**

#### The 6th Small Systems Simulation Symposium

Niš, Faculty of Electronic Engineering, 12-14 February, 2016

# **Contents**

## **Plenary Sessions**

| P1 <b>Sin</b> | non Le Blond and Vančo Litovski, A Mechanism for Collaboration Between Industry and Academia in the UK                                                    | 1-7     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| P2 <b>Dra</b> | agan Domazet, Co-operative Education Programs with IT Companies at Belgrade  Metropolitan University                                                      | 8-15    |

| Mode          | eling 1                                                                                                                                                   |         |

| M1.1          | Simon Le Blond, Brian Ross and Vančo Litovski, On the Implementations of Circuit Models of Arcs                                                           | . 16-21 |

| M1.2          | Vazgen Melikyan, Ararat Khachatryan and Davit Mirzoyan, Self-Heating Assessment for Interconnects During ESD Event                                        | . 22-25 |

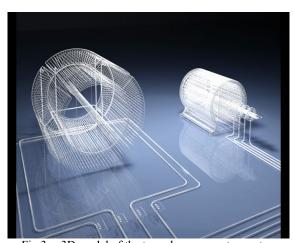

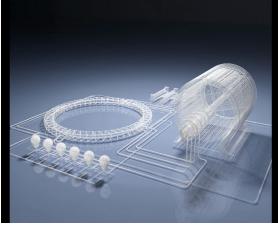

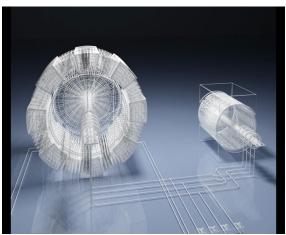

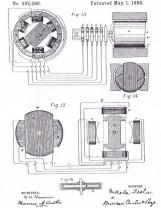

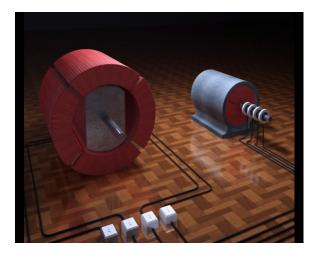

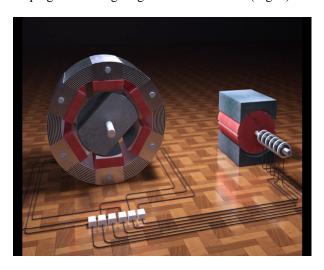

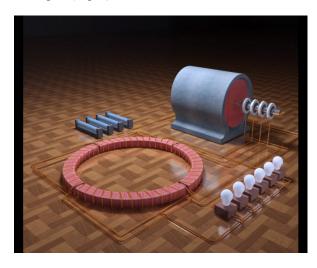

| M1.3          | Vladan Vučković, 3D Modeling and Simulation of the Tesla's Polyphase Generators and Motors                                                                | . 26-31 |

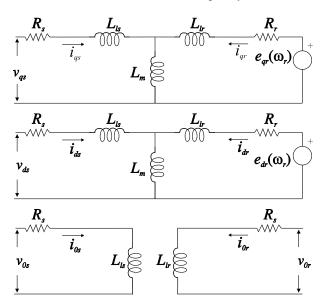

| M1.4          | Nebojša Mitrović, Vojkan Kostić, Milutin Petronijević and Bojan Banković, Pspice<br>Model for Three Phase Induction Motor                                 | . 32-35 |

| M1.5          | <b>Bojan Banković, Nebojša Mitrović, Vojkan Kostić and Milutin Petronijević,</b> <i>Pspice Simulation of Power Electronics and Induction Motor Drives</i> | . 36-39 |

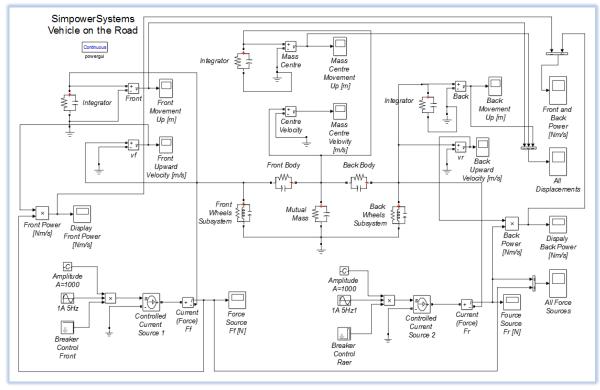

| M1.6          | Milan Simić, Vehicle Modelling Using Physical Networks                                                                                                    | . 40-45 |

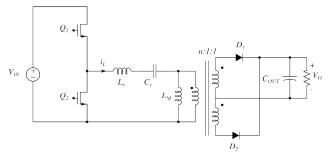

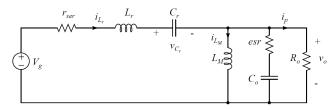

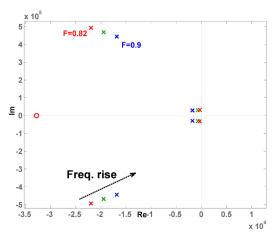

| M1.7          | Milan Pajnić, Miroslav Lazić and Zoran Cvejić, Small Signal Modeling of Series-<br>Parallel Resonant Converters Based on Extended Describing Function     | . 46-49 |

| Mode          | eling 2                                                                                                                                                   |         |

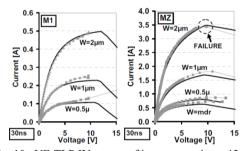

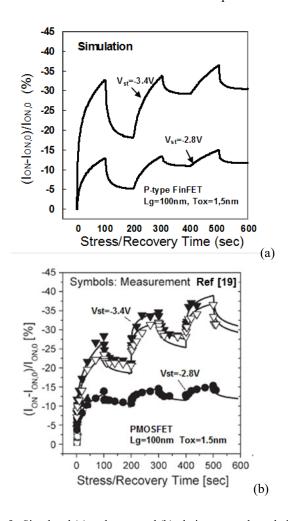

| M2.1          | Nebojša Janković, Chadwin D. Young and Miloš Marjanović, Spice Simulations of Aging Effects in Double-Gate FinFETs                                        | . 50-53 |

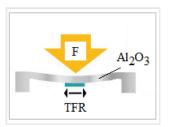

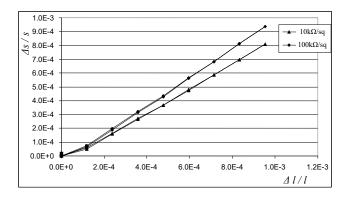

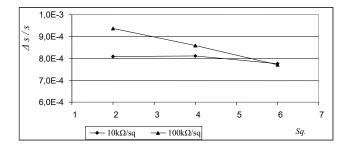

| M2.2          | Ivanka Stanimirović and Zdravko Stanimirović, Modelling and simulation of standard TFRs as strain sensing elements                                        | . 54-57 |

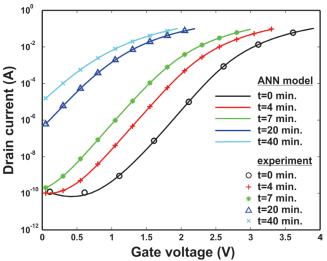

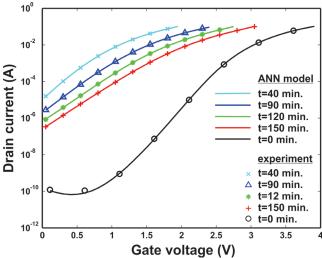

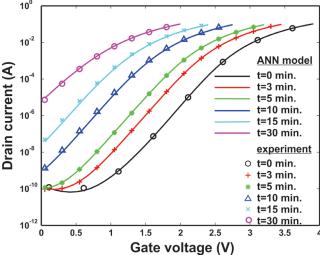

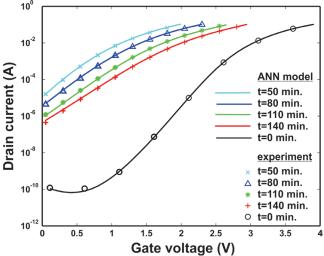

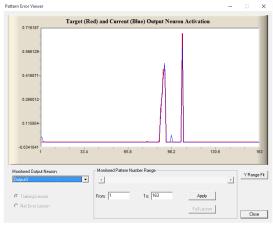

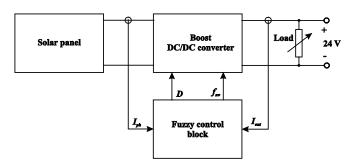

| M2.3          | Aleksandar Vulović, Milan Savić, Sanja Aleksić and Dragan Pantić, ANN Model of High Electric Field Stress in n-channel VDMOS Power Transistors            | . 58-61 |

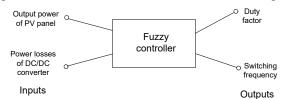

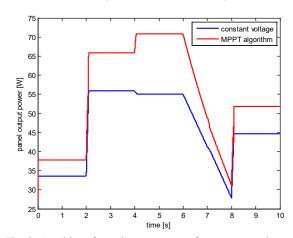

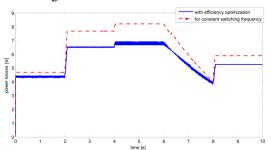

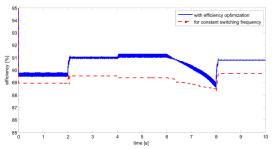

| M2.4          | <b>Duško Lukač and Miljana Milić</b> , ANN solution for increasing the efficiency of tracking PV systems                                                  | . 62-66 |

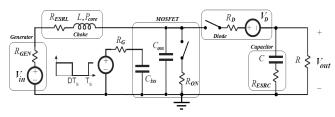

| M2.5          | Branko Blanuša, Željko Ivanović and Branko Dokić, Model of High Efficiency Solar System with DC/DC converter                                              | 67-71   |

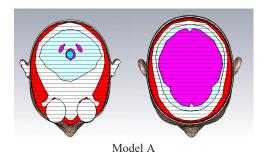

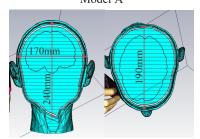

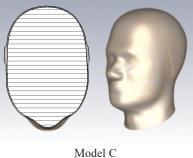

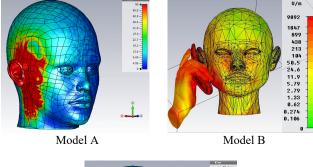

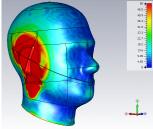

| M2.6  | <b>Dejan Jovanović, Vladimir Stanković, Dejan Krstić and Nenad Cvetković</b> , <i>Modelling SAR of Mobile Phone Inside User' Head</i>                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M2.7  | Aleksandra Panajotović and Dragan Drača, Outage Probability of SC Receiver  Operating in Both Microcell and Picocell Environment                                     |

| Syste | m Design and simulation                                                                                                                                              |

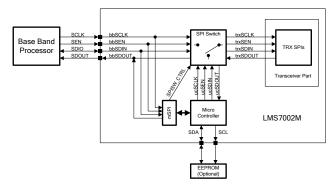

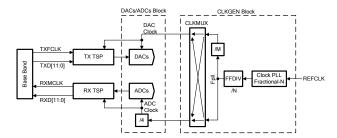

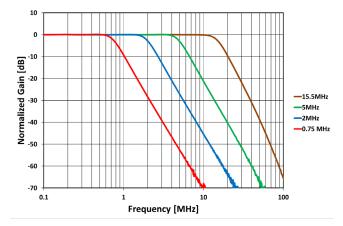

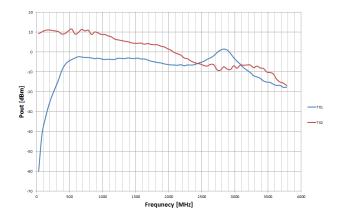

| S1.1  | <b>Srđan Milenković</b> , LMS7002M FPRF 2x2 MIMO Transceiver IC with High Digital Content                                                                            |

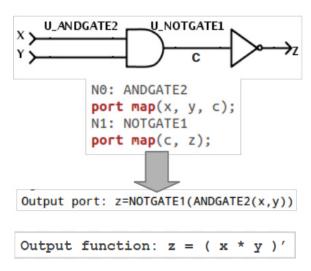

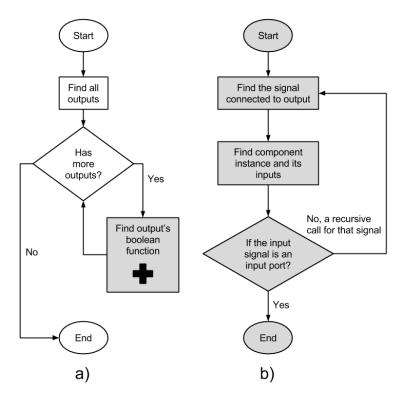

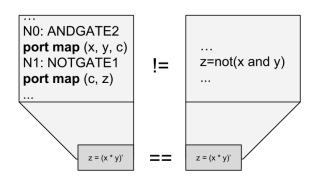

| S1.2  | Vladimir Zdraveski, Andrej Dimitrovski and Dimitar Trajanov, Improving HDL Higher<br>Level Logical Analysis Using Boolean Function Feature                           |

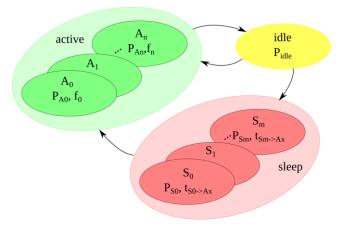

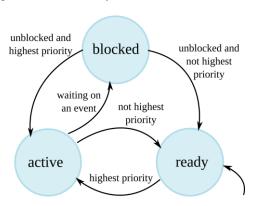

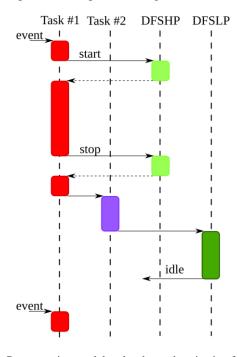

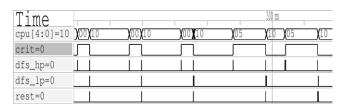

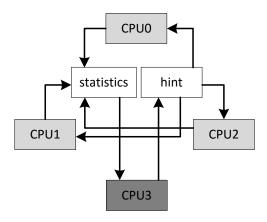

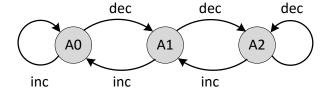

| S1.3  | Strahinja Janković, Dragomir El Mezeni, Vladimir Petrović, Ivan Popović, Jelena Popović-Božović and Lazar Saranovac, EASYSim: Energy-aware embedded system simulator |

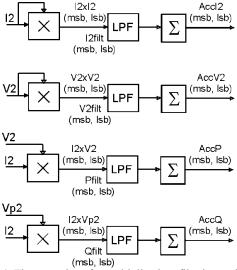

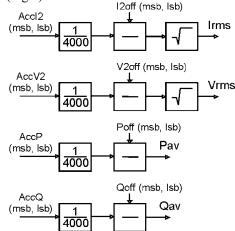

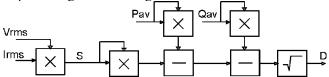

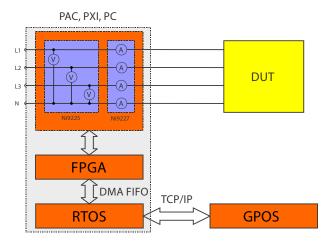

| S1.4  | <b>Borisav Jovanović, Predrag Petković and Milunka Damnjanović</b> , The Power Quality Estimation by Integrated Power Meter DSP Block                                |

| S1.5  | Dejan Stevanović, Marko Dimitrijević, Miona Andrejević Stošović and Predrag Petković, Monitoring and Compensation of Harmonics in Smart Grid                         |

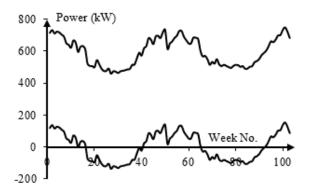

| S1.6  | Jelena Milojković, Slobodan Bojanić, Octavio Nieto, and Vančo Litovski, One-Week-<br>and One-Month-Ahead Prediction of Suburban Electricity Load                     |

| Circu | it design and simulation                                                                                                                                             |

| S2.1  | Branko Dokić, Miladin Sandić, Energy – Efficient CMOS Full Adders                                                                                                    |

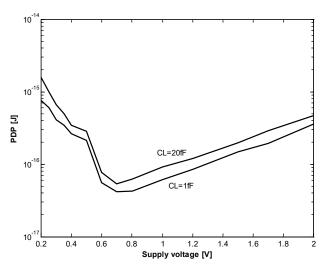

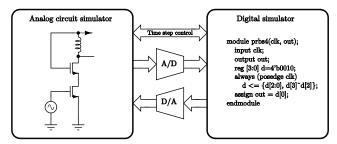

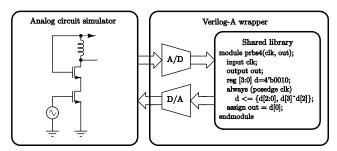

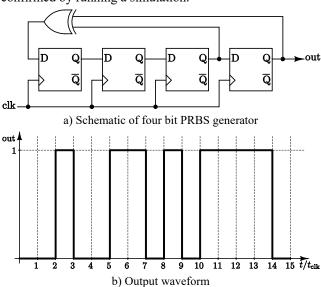

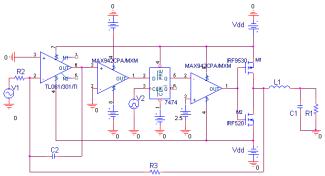

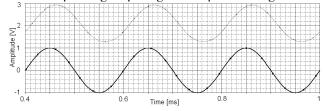

| S2.2  | Dušan N. Grujić, Mihajlo Božović, Pavle Jovanović, Milan Savić, and Lazar<br>Saranovac, Periodic Steady State Simulation of Mixed-Signal RF Circuits                 |

| S2.3  | Nazeli Melikyan, Method of Statistical Timing Analysis with Uncertainty                                                                                              |

| S2.4  | <b>Dejan Mirković, Miona Andrejević Stošović and Vančo Litovski,</b> <i>Exploring Second Order s-to-z Transformation for IIR Linear Phase Filters Design</i>         |

| S2.5  | Dragan Topisirović, Miona Andrejević Stošović, and Vančo Litovski, CMAC and Chebyshev Filters in Frequency Domain                                                    |

| S2.6  | Jovan Galić, Tatjana Pešić-Brđanin and Lejla Iriškić, Class-D Audio Amplifier using Pulse Width Modulation                                                           |

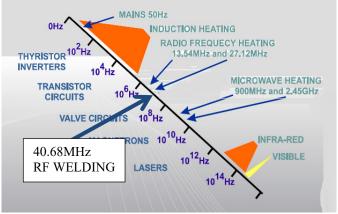

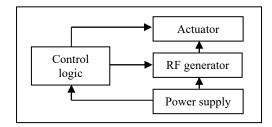

| S2.7  | Dušan Petrović and Predrag Petković, Design of RF power amplifiers at 40.68 MHz 137-142                                                                              |

| S2.8  | Miljan Petrović and Miljana Milić, Response Distribution Analysis for Oscillator<br>Circuit Due to Process Variation                                                 |

# A Mechanism for Collaboration Between Industry and Academia in the UK, Exemplified by Project SYNAPS

#### Simon Le Blond and Vančo Litovski

#### Invited paper

Abstract – Whilst often working in separate silos, there are huge rewards in effective collaboration between industry and academia. Complex modern engineering challenges also necessitate working within a team of teams – meta-team-working. We exemplify how academic and industrial collaboration combined with meta-team-working may be leveraged through the Innovate UK Energy Catalyst funding mechanism, specifically project SYNAPS, a technically challenging project focussed with smart low-voltage power distribution networks with a heavy simulation component.

Keywords - Research funding, collaboration, power network simulation.

#### I. Introduction

Within the engineering world, the path of least resistance is for industry and academia to operate in very separate silos. Often this is down to conflicting goals: the key performance metric for academic career progression is to disseminate new knowledge through publication, whereas industry must protect and monetise intellectual property. For these reasons among others, academics and industrialists can have very different mind-sets, attitudes and beliefs that can make collaboration problematic.

However, there are potentially huge rewards from close collaboration. Deep specific, fundamental and focussed knowledge in a particular field can be transferred, applied and commercialised through the right partnership. Moreover specialist *real world* knowledge, for example that which is commercial and regulatory as well as technical can inform and direct fundamental research. So the best functioning partnerships therefore become mutually beneficial and symbiotic.

It is a truism to say that well into the twenty first century much of the easy advances - the *low hanging fruit,* in science and engineering has already been picked. One just has to look at increasing trend in numbers of authors on scientific publications to conclude that even incremental breakthroughs require large collaborations of many researchers from a range of disciplines. A recent paper from CERN regarding the Higgs Boson set the record at over 5000 authors [1]! In the information age, our complex

Simon Le Blond and Vanco Litovski are with the Department of Electronics and Electrical Engineering, University of Bath UK, s.p.leblond@bath.ac.uk

modern world relies as much on the division of expert knowledge as the production lines that drove the industrial revolution relied on the division of labour. Complex modern engineering problems often require This is the harmonious, channelled Engineering. application of knowledge and expertise from a number of specialist entities to achieve a specific outcome or set of interrelated outcomes. This structured meta-team working is contrary to the pressure to appoint and retain "research stars" in academia; well known personalities that give kudos to an institution, helping to accrete funding and students. However it is also true that the contribution from one particular individual can far outstrip the combined contributions of many, particularly in innovation: a study [2] concluded there was an approximate variation in productivity in programmers of 20:1. Going further, Bill Gates is, (perhaps apocryphally) accredited for asserting "A great lathe operator commands several times the wage of an average lathe operator, but a great writer of software code is worth 10,000 times the price of an average software writer." So star individuals can play a role in providing a step change if they are lucky enough to occupy the tail end of the Boltzmann-like distribution of ability: they achieve the escape velocity necessary in the way that the combined efforts of others will not.

In academia the analogy can be thought of like a theatre company where the stars are equally important, if not more so, than those doing the directing and producing. In this paradigm those off stage cannot necessarily do the job of the actors, in the same way that a research manager may not have the expertise to conduct the work of the researchers (s)he is supervising. In engineering industry the structure is much more hierarchical such that those at higher levels normally have the skills and knowledge to do the work of those below them. They are therefore given greater responsibility (and remuneration) and solve complex outcomes through divide and conquer - breaking up small parts of the problem onto complex Gantt charts and allocating the human resource appropriately. Since there are advantages to both paradigms, their hybridisation when academia and industry meet can be very effective and also lead to better understanding and new ways of operating for both parties. For the very same reasons, these two world views can lead to tensions particularly between researchers and industry executives who at first have little mutual empathy due a lack of understanding about the pressures they face.

This paper presents a high level discussion of the Innovate UK / EPRSC mechanism for collaboration in the hope that it will provide a useful template at various levels of scale for those faced with catalysing a functional symbiosis between industry and academia.

The SYNAPS (Synchronous Analysis and Protection System) project is an Energy Catalyst Mid-Stage Innovate UK/EPSRC project aiming to developing smart grid technologies to the low voltage power distribution network. Within SYNAPS the authors are responsible for delivering a work package with a heavy power system simulation component. We use the SYNAPS project to exemplify how academic-industrial collaboration may be orchestrated. In particular we examine the key players in the UK power industry, those at the vanguard of the smart grid, both external and within the consortium and how good working relationships can be forged amongst these entities.

The rest of the paper is organised as follows. In section 2 we discuss the general funding ecosystem going into more detail over SYNAPS funders, Innovate UK and EPSRC. In section 3 we examine the UK power industry. In section 4 we introduce the SYNAPS project with a brief technical overview, and in section 5 discuss how collaboration inside and outside can achieve the ambitious technical goals by meta-teamwork. Finally we draw some general conclusions.

#### II. UK RESEARCH FUNDING ECOSYSTEM

#### A. General Overview

In the UK, funding for research innovation comes from many sources, although this section is written from the perspective of the authors, academics in electronic and electrical engineering. With this in mind, our main funding sources are:

#### • Research Councils UK [3]:

An umbrella organisation for 7 broad discipline focussed UK academic research councils, with those particularly relevant to electrical engineering being EPSRC, (Engineering and Physical Sciences Research Council) NERC (National Environment Research Council and STFC (Science and Technology Facilities Research Council). These bodies use specifically scoped calls alongside standard "responsive mode" with open scope, both awarded through a rigorous peer review process, usually including a panel stage.

- European Research Council (ERC) [4]: European Union Funding, currently migrating from Framework Programme 7 to Horizon 2020 [reference website]. European funding rules often necessitate consortia of many partners both academic and industrial across at least 3 EU countries so rely on large critical mass to be viable.

- Direct Funding from the UK Government: Various government departments may commission targeted research calls.

#### • Innovate UK [5]:

An executive non-departmental public body sponsored by the government department for Skills Business and Innovation set up to de-risk research and development.

- Collaborations with various partner research councils across the globe, usually focussing on mobility and seed funding.

- Finally an industrial partner may outsource research to an academic institution if they are unable to undertake it internally.

With the exception of the international and private sources, the UK Government pays into these expert bodies to distribute money as they see most appropriate, so in some sense, the UK Tax Payer is the ultimate source of most research funding. Clearly public money must be used responsibly and thus the research from these areas is subject to the highest levels of scrutiny: both auditing, monitoring and reporting throughout the grant lifecycle to ensure the funding is being used effectively.

The particular funder that one targets for a grant proposal is highly dependent on the type of work, the research outcomes and the parties required to achieve these, in addition to the stage of career of the principal investigator. A pure research project in engineering may be most directly suited to EPSRC funding, whilst one closer to commercial application would be more relevant to either Innovate UK or ERC. Moreover it is unlikely that grant reviewers will entrust large sums of money to early stage career researchers without an established track record, regardless of the merit in their idea.

#### B. EPSRC

EPRSC (Engineering and Physical Sciences Research Council) is the UK's main agency for funding research in engineering and the physical sciences, investing up to £800M p.a. in research and postgraduate training [6]. It is the primary source of funding for pure physical sciences research more blue sky "engineering research" and is thus the first stop for academics who wish to fund a research project confined within their own institution or with one or more academic partner institutions. EPSRC's strategic plan [7] informs on "grow" "maintain" and "reduce" subject areas within the portfolio and thus the case for supporting a particular grant can be enhanced if it aligns with EPSRC's overall strategy.

#### C. Innovate UK

According to their Website, Innovate UK is "the UK's Innovation Agency" [5]. Their remit is to

- determine which science and technology developments will drive future economic growth.

- meet UK innovators with great ideas in the fields Innovate UK are focused on.

- fund the strongest opportunities.

- connect innovators with the right partners they

need to succeed.

• help innovators launch, build and grow successful businesses.

#### D. Energy Catalyst

Energy globally is regarded as a major societal challenge – the compounding problems of climate change, limited fuel resources (and their increasingly uncertain supply chains) increasing population, global industrialization and the accompanying load growth combine to form an "energy crisis" that is one of the greatest existential threats to human civilization. On the other hand, the UK government recognizes that there is huge global commercial opportunity for UK plc in meeting this challenge.

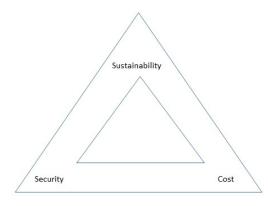

The Energy Catalyst is a rolling funding scheme overseen by Innovate UK to support technology projects addressing all three corners the "Energy Trilemma": the competing need to reduce emissions, improve security of supply and reduce costs (see Fig.1.) There are three tiers of funding awards: early stage, mid stage and late stage with funding capped at £300 K for early feasibility studies, £3 M for mid-stage technology development and £10 M for pre-commercial technology validation respectively. Mid stage and late stage must be business led and collaborative but may involve academic partners or any other research organisation who are permitted to absorb up to 30% of total project allocation. Crucially, the funding for academic partners comes from EPSRC and is funded at 80% Full Economic Costs (which in the author's world is synonymous with "fully funded" due to the complex array of overheads that RCUK are willing to fund and those that they are not). Innovate UK defines the separate players in this ecosystem as 1. Research institution, 2. Small/micro SME (Small Medium Enterprise) 3. Medium SME and 4. Large Business. This demarcation points are summarized in table 1 which also shows the level of match-funding that each entity must contribute themselves.

It is worth explicitly noting, with reference to table 1, that with these carefully graded funding rules, the industrial partner must match fund a portion of their own project costs with a higher percentage investment the closer they are to commercial readiness, such as to drive the eventual commercial exploitation of the project IP. Also, since the research institution is not expected to commercialise their IP they are not asked to risk the match funding. The negotiation of Collaboration Agreements between all partners is necessarily complicated as it must allow for the free flow of information between the partners to collaborate in the project, but also simultaneously protect the commercial interests of the industrial partners and the academic partner's remit to disseminate research outcomes. Innovate UK therefore supplies a template Collaboration Agreement to assist SMEs that may not have access to, or the resource, to outsource legal assistance. In addition it is vital all partners must be under NDA (Non-Disclosure Agreement) in order to even begin working on the proposal, let alone the project itself. Despite these safeguards, all partners, particularly the SMEs are exposed to a high level of commercial risk through leaked IP, whether by design or by accident. It is therefore imperative that partners behave with impeccable business ethics and build up mutual trust at the consortium building stage before embarking on a project.

Fig. 1. The "energy trilemma" illustrating the competing needs in the energy crisis to reduce emissions, improve security of supply and reduce costs. It is very difficult to meet one or two of these without compromising heavily on the third.

#### III. UK Power Industry

Before discussing Project SYNAPS it is necessary to briefly summarise the UK Electrical Power Industry. The UK power industry was globally one of the first utilities to be privatised in 1990. Since then, the national transmission grid, the supply side and the regional distribution networks have all been operated and owned by private entities.

TABLE I ENERGY CATALYST FUNDING TIERS

| Scheme         | Total funding<br>available | Research<br>Institution               | Small SME<br><50 people,<br>turnover £10 M | Medium SME < 250 people, turnover £50 M | Business |

|----------------|----------------------------|---------------------------------------|--------------------------------------------|-----------------------------------------|----------|

| Early<br>Stage | £300 k                     | 80% FEC<br><50% total<br>project cost | 70%                                        | 60%                                     | 50<br>%  |

| Mid<br>Stage   | £3 M                       | 80% FEC<br><30% total<br>project cost | 70%                                        | 60%                                     | 50<br>%  |

| Late<br>Stage  | £10 M                      | 80% FEC<br><30% total<br>project cost | 45%                                        | 35%                                     | 25<br>%  |

The UK government recognizes that the overseers of generation, transmission and distribution necessarily hold natural monopolies and thus appoints a regulator - *Ofgem* - to protect consumers. Businesses can be liable for heavy financial penalties for any breach of contract or exploiting their monopoly.

Suppliers or retailers are companies that purchase electricity on the wholesale markets from generators and then sell it to customers - commerce, industry and domestic alike. Most UK consumers have a vague notion that retailers are those responsible for getting electricity to their power sockets. However this role is fulfilled at a national level by National Grid, the Transmission System Operator (TSO) and then at a regional level by the eight Distribution Network Operators DNOs, who are collectively responsible for the operation and maintenance of the electrical power network infrastructure. Electrons are not so discerning of these arbitrary boundaries so power flows at light speed down wires using alternating current at a system-wide nominal frequency of 50 Hz. The High Voltage Transmission Network and can be thought of the highways whilst the distribution network at lower voltages are the trunk roads all the way down to individual There is presently a trend towards driveways. decentralization of energy infrastructure to better facilitate low carbon economy. Historically, the system was designed around large centralized thermal based power plant. Many cleaner energy sources and energy storage technologies suit connection at lower voltage levels and therefore the distribution networks are becoming more active with bi-directional power flows, with microgenerators selling their power back to the grid as well as consuming it. Contrary to this drive, ageing infrastructure is being pushed well beyond its expected lifetime leading to a huge asset management problem, particularly within the oldest parts of the network: the low voltage (LV) distribution network. This puts two fold pressure on the LV voltage network – the requirement to modernize the aging assets and the requirement to modernize into a "smart grid" to accommodate connection of new energy technologies. This also creates a massive business opportunity in LV networks.

#### IV. PROJECT SYNAPS – TECHNICAL OVERVIEW

Project SYNAPS (SYNchronous Analysis and Protection System) is a £1.7 M Innovate UK energy catalyst mid-stage project currently underway, addressing the problem of LV network modernisation directly by developing an array of inter-related Smart Grid LV network technologies. In this section we will give an overview of its technical themes.

#### A. Higher network visibility

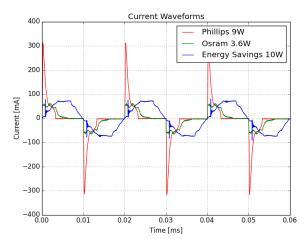

Essentially the core SYNAPS technology will be a way of monitoring network conditions at extremely high

granularity. This involves measuring the physical quantities of voltage and current waveforms in the 415 V three phase network at high sample rates (~200 kHz) and then inferring knowledge about the network in real time or near real time. This unlocks a whole host of new functionality. For example, a big issue for network operators is knowing the topology of the LV network itself. Like capillary level blood vessels in the human body, the LV network is vast and sprawling and often "multiply patched" since over time it has grown sub-optimally and organically, following the incremental growth of the built environment. DNOs therefore often have poor historical records of exactly what assets they have at LV. SYNAPS will develop a monitoring platform able to infer network topology.

#### B. Pro-active Maintenance

A particular problem is progressive water ingress into cable insulation causing arcing short circuit faults. This often initially causes an intermittent fault that does not always melt the protective fuse but nonetheless risks damage to connected equipment. The DNO only has knowledge about this problem when the fuse eventually does operate, and customers call in to complain they have lost supply. The DNO responds by physically sending maintenance personnel out to replace the fuse. If the fault persists the fuse will then operate again necessitating digging the cable up and replacing it. This cumbersome process leads to many customer minutes off supply and large financial penalties to the DNO from the regulator. SYNAPS will be able to use pattern recognition techniques to detect early when an intermittent fault will occur and thus maintenance can be proactively organised to avoid customer minutes lost.

#### B. Protection and reconfiguration

The protective fuse is itself a very crude device. It only operates once before requiring replacement and its operating characteristic is limited to an inverse time-overcurrent. At higher voltage levels the network is protected by circuit breakers that use sophisticated fast digital relaying algorithms to operate in milliseconds following a fault, overseen by carefully coordinated settings of the overall protection system. This approach keeps as much of the healthy system live whilst isolating the faulted part. SYNAPS will apply this paradigm to the LV network.

With a partially meshed or fully meshed network, there is the possibility of routing power from a different source and thus bringing customers back on supply before a permanent fault can be fixed. There are complex safety and technical implications that must be considered before doing this. With regard to the technical, low carbon stresses such as micro generation and electric vehicles will make the situation more complex: for example if they remain connected under faults they can potentially create an

unintentional islanded network. SYNAPS will consider these aspects and develop new reconfiguration algorithms for the LV network.

#### C. Solid state switchgear

An important gateway technology at LV would thus be replacement for the fuse: a switch that can be tele-operated and that can interrupt heavy short circuit currents that arise under fault conditions. SYNAPS is thus researching and developing solid-state switchgear than can operate much faster than electromechanical devices by using power electronics. Regardless of the final choice of technology, the ability to tele-operate SYNAPS switchgear will unlock much more sophisticated protection and reconfiguration algorithms.

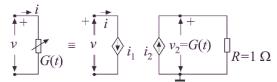

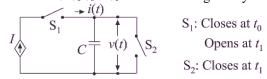

#### D. Network Simulation

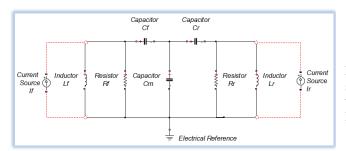

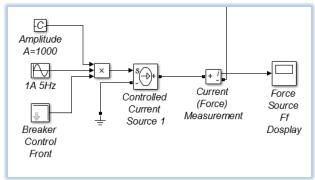

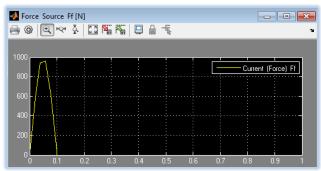

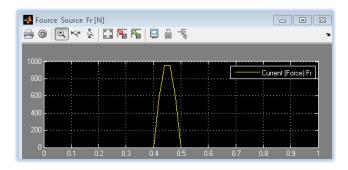

Real world fault data on actual systems is scarce because these systems are not monitored and live tests are expensive, disruptive and dangerous. Therefore in achieving the SYNAPS outcomes there is an overarching requirement to simulate various fault scenarios in the LV network in high levels of detail. The authors are thus tasked with time domain simulation of various LV network topologies. In the first stage this involves simulating fault waveforms "offline" with tools such as SPICE and ATP-draw (the modern graphical version of EMTP) to conduct electromagnetic transient simulation, to create waveform data that can be fed into to machine learning inference engines. In the second stage the simulations must be in real time such that the developed SYNAPS platform can be tested and validated.

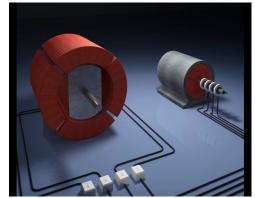

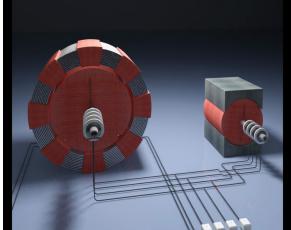

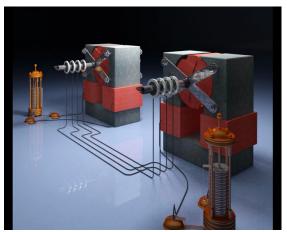

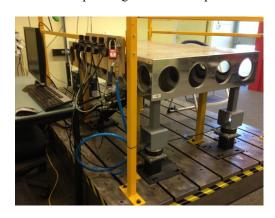

The RTDS is a power network simulation hardware tool that allows any power system to be digitally simulated in real time at a base time step of 50 µs, confined only by the amount of modular processing power available [8]. See figure (2). The RTDS has the very powerful feature of putting hardware into a closed loop in the simulation through various I/O ports. In more detail the RTDS can simulate the power system, synthesising real voltages and currents as they vary with time using digital to analogue conversion and then send these signals to outboard equipment – in this case, the SYNAPS platform. The SYNAPS equipment can do the required processing and then send analogue or digital signals back to the RTDS, automating network tasks. This could be opening or closing a switch following a fault, for example. Due to the aforementioned difficulties in real world testing, this step is a vital test and validation task before utilities are comfortable deploying SYNAPS on a real power network.

An interesting technical challenge in SYNAPS is digitally simulating the electrical fault are – the high channel of ionised plasma when an insulating medium breaks down - which is a complex physical phenomenon [9]. This involves computing the time varying are

conductance in every timestep using differential equations. Interested parties are referred to the paper in the SSSS conference proceedings by the same authors confined to this very subject that develops a new model specifically for arcs propagating through cable insulation [10].

#### V. PROJECT SYNAPS – THE CONSORTIUM

A technically ambitious and complex project such as SYNAPS requires an array of various specialisms to be channelled and focussed into a concerted harmonious

Fig. 2. The RTDS (Real Time Digital Simulator) allows real time simulation of Power networks and can connect hardware in the loop.

effort. This is a kind of *meta-teamwork* in as much as it requires a team of teams. Within the consortium we therefore have assembled three companies, classified under Innovate UK as micro-SMEs, and two partner universities. In addition a large established micro-processor manufacturer is offering contribution in kind with chip development platforms in line with a strategic view onto the smart grid market.

The industrial project partners are:

#### • Power Line Technologies (Project leaders)

PLT designs, manufactures and markets solutions in the smart grid and communications market place. The Company has expertise in LV & MV smart grid, telecommunications, powerline communications and network management. It has already established relationships with distribution and transmission network operators for its solutions.

#### • Akya Ltd

Akya Ltd are responsible for developing the chips that will process the SYNAPS data. Akya specialises in the

development of advanced bespoke digital signal processing solutions for high performance and / or low power devices. Akya's ART technology is capable of providing highly-optimised, application-specific, fully programmable DSP cores with a power/performance far better than that which can be achieved by conventional general-purpose DSP designs.

#### Techna Ltd

Techna are producing the SYNAPS LV switch gear. With over seventy years of electrical engineering experience Techna are specialists in advanced circuit protection products.

The academic partners are:

- University College London (Department of Mathematics and Statistics) are developing the machine learning algorithms that will take LV network data and infer information about the network.

- University of Bath, Centre for Sustainable Power Distribution (CSPD) is contributing its expertise in real time digital simulation and transient based protection to generate fault data to validate the SYNAPS platform. (The authors of are from the University of Bath.)

Since SYNAPS is a truly collaborative project, there is necessarily much interdependency between the partner work packages. For example it is important that the simulation data is supplied on time, and that developed software algorithms can be delivered in a form to run on the SYNAPS hardware. All deliverables are therefore synched to a common time grid of quarterly milestones over the 2 year project lifespan.

It is also vital therefore to establish good working relationships, clear channels of communication and regular reporting between the partners. In addition due to the modest size of the industrial partners, many of those involved must fulfil both a high level executive role and a detailed technical engineering role.

Formal project meetings may therefore become too large and unwieldy for detailed intimate technical discussions that concern only two or three partners. Therefore to facilitate cross-partner technical work there are three technical coordination groups (TCGs) with a different focus and combination of membership of the relevant project partners. The TCGS favour small and agile working between technical personnel (or those fulfilling their technical role) within different partner entities. To facilitate this inter-partner collaborative working various web based software tools are invaluable. For example Skype is ubiquitous free software for VoIP conference calls. However Cisco's WebEx also allows screen sharing and meeting recording across multiple remote guests and user. The Confluence software by Atlassian allows a web based focal project repository of documents, media and meeting minutes to be shared and edited collaboratively. However none of these can currently replace the nuances of a physical face to face meeting, so often it is necessary to travel and it is important partners distribute the burden of travel and hosting fairly across the consortium. All other things being equal, it is perhaps therefore better to choose partners that is within a reasonable distance. Face to face meetings are a great opportunity to conduct partner site visits and socialise (with the help of appropriate choice food and beverage of course to lubricate and celebrate progress).

SYNAPS brings together engineers from different disciplines that have a slightly different technical vocabulary. Computer science (hardware and software), electronics engineers, mathematicians and electrical engineers have a lot of overlapping knowledge but the Venn intersection clearly does not cover the specialist knowledge within each discipline. (If it did there would be no added value in meta-team work...) It is therefore vital that the partners have empathy for different levels of technical knowledge and understanding within the consortium, and tread the fine line between informing and condescension when explaining concepts to non-expertcolleagues. However this is also a great opportunity, not just acquiring complementary knowledge from a different discipline but also enhancing understanding of one's own. In academia the symbiosis between the pillars of teaching and research is mutually reinforcing because being able to teach and explain a high level concept necessities the highest form of understanding in the teacher. Like students, colleagues from different disciplines can often ask uncomfortable fundamental questions that can helpfully critique an idea for feasibility and robustness; a question that might not occur to an expert peer in the same area due to mutual assumed knowledge.

In order to succeed the SYNAPS consortium must interface with various external power industry organisations. In particular, close working with DNOs (Distribution Network Operators) is necessary to acquire technical data and also scope market requirements since the DNOs will be the main customers of any commercial offering. Here too empathy and emotional intelligence is required. Utilities have a huge challenge maintaining and operating the network within regulatory limits with limited human technical and financial resources. Therefore in acting responsibly they are understandably wary of any new technology due associated risk and large learning curve. This results in an extremely conservative industry, where simple elegant design is preferred over feature laden sophistication. Whilst power systems technology may appear to evolve at a glacial pace to engineers with an ICT background, it is important to remember the utilities must maintain a complex interconnected system with 100% reliability and safety. The consequences of a smart phone widget failing are rather less drastic than a transformer protection relay failure. One leads to an angry customer review whilst the other leads to a substation explosion, customers without power and potential loss of life. The DNOs have unequalled intimate knowledge of the interrelatedness of their networks and the resulting design philosophy which should be respected all costs. It is therefore necessary for SYNAPS to engage with utilities early establishing rapport for functional partnerships founded on mutual respect and empathy. This of course extends to any technology project where the end users are not within the consortium: regular engagement with the customers from the start is vital.

#### CONCLUSION

This paper has discussed the merits of collaboration between academia and industry and coined a new expression *meta-team-working* — working in a team of teams. Interdisciplinary *meta-team-working* is needed to solve complex modern engineering challenges. For successful *meta-team-working* the ways of operating, cultures and vocabulary must be respected and understood. The very same challenges also bring great opportunity for widening the horizons for all those involved.

We have exemplified this thesis though the innovation funding ecosystem in the UK and in particular the Innovate UK Energy Catalyst project SYNAPS which is developing smart grid technology in LV power networks. Here as with all such projects there is need for effective communication, empathy and mutual respect, in all directions within the organisational model.

#### ACKNOWLEDGEMENT

This work is funded by EPSRC under the Innovate UK Energy Catalyst project, SYNAPS (SYNchronous Analysis and Protection System). The authors gratefully acknowledge the joint financial support of EPSRC and Innovate UK and use of facilities and services at the University of Bath, UK.

#### REFERENCES

- [1] A. Collaboration, C. M. S. Collaboration, G. Aad, B. Abbott, J. Abdallah, O. Abdinov, *et al.*, "Combined Measurement of the Higgs Boson Mass in \$pp\$ Collisions at \$\sqrt{s}=7\$ and 8 TeV with the ATLAS and CMS Experiments," *Physical Review Letters*, vol. 114, p. 191803, 05/14/2015.

- [2] B. Curtis, "Substantiating programmer variability," *Proceedings of the IEEE*, vol. 69, pp. 846-846, 1981.

- [3] Research Councils UK website http://www.rcuk.ac.uk/ (last accessed December 2015)

- [4] Eurpean Research Council https://erc.europa.eu/ (last accessed December 2015)

- [5] Innovate UK website https://www.gov.uk/government/organisations/innovate -uk/about (last accessed December 2015)

- [6] EPSRC Engineering and Physical Sciences Rearch Council https://www.epsrc.ac.uk/ (last accessed

- December 2015)

- [7] EPSRC Engineering and Physical Sciences Rearch Council https://www.epsrc.ac.uk/about/plans/strategicplan/ (last accessed December 2015)

- [8] P.A. Forsyth, D. Shearer, D. Rydmell, "Testing Firing Pulse Controls for a VSC-based HVDC Scheme with a Real Time Timestep  $< 3 \mu s$ ," presented at the IPST, 2009.

- [9] H. A. Darwish and N. I. Elkalashy, "Universal arc representation using EMTP," *Ieee Transactions on Power Delivery*, vol. 20, pp. 772-779, Apr 2005.

- [10] Our paper?

# Co-operative Education Programs with IT Companies at Belgrade Metropolitan University

#### Dragan Domazet

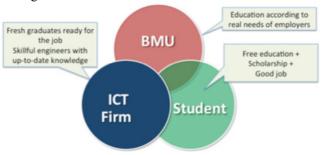

Abstract - In this paper a description of the cooperative educational program of Belgrade Metropolitan University is described. It implements a parallel co-op model as students simultaneously follow regular courses and work. The BMU Co-op model provides students with paid tuition fees, scholarships and the prospect of a job after graduation. An IT company also has many gains by providing these benefits to students. It can employ a group of graduated IT students each year, specially educated for the company, as these graduated students, its scholars, have four years of work experience in the given company during their studies.

Keywords – Cooperative education, education of IT and software engineering students, internship

#### I. INTRODUCTION

IT companies these days often have difficulties to recruit new engineers with needed knowledge and skill sets. The demand is high and the offer of fresh graduated students is not sufficient and furthermore, in many cases not in line with requirements of employers. Due to the high demand of IT engineers, many students start working even before completing their studies. This may have a negative impact to their professional development. On the other hand, companies need to provide additional training to these employed students to solve their short-term problems. However, doing this in many cases creates long-term problems, as these programmers usually never complete their studies and have limitations of their capabilities due to poor and uncompleted education.

Having these challenges in mind, Belgrade Metropolitan University (BMU) has developed a parallel cooperative program for students of its bachelor program in Information Technology, Software Engineering, Game Development and Information Systems. Cooperative educative programs are very popular and developed in Canada [1-4] and USA [5-7], but the cooperative program of BMU has some specific features that will be described in the paper.

#### II. THE CONCEPT OF THE BMU CO-OP PROGRAM

#### A. Periods of Work and Duration

Dragan Domazet is Professor and Rector of Belgrade Metropolitan University, Tadeuša Košćuška 63, 11000 Belgrade, Serb ia. E-mail: dragan.domazet@metropolitan.ac.rs

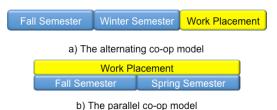

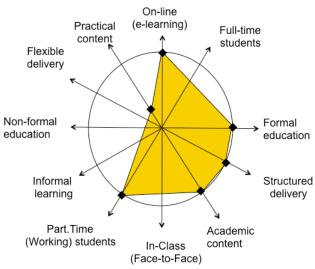

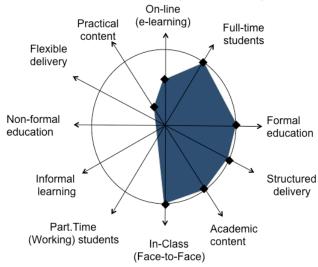

Cooperative education is a partnership between a university's academic programs and professional employers who provide off-campus work experience. It is a structured way of learning that combines in-class learning with periods of actual work. There are alternating and parallel co-op models. In the alternating co-op model students alternate a semester of academic coursework with an amount of time working, repeating this cycle several times until graduation (Fig. 1.a). The parallel method splits the day between school and work, typically structured to accommodate the student's class schedule (Fig. 2.b). Surveys and analyses [8-11] have reported many benefits for students that cooperation education can provide.

Fig. 1 The alternating and parallel co-op models

The co-operative education program of BMU implements the parallel co-op model. Students follow regular courses having at least 20 in-class hours a week and up to 20 work hours in a company.

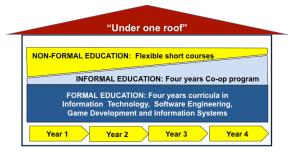

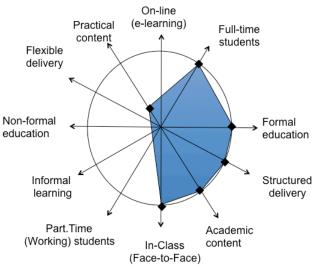

During their four-year academic bachelor education, their amount of work in companies is slowly increasing along with their capability to accept more demanding work assignments. During periods of their work, they initially might have more special, short training courses aiming to provide them company-specific know-how (non-formal education), but later they learn more by getting experience in performing their work assignments (informal education), as shown in Fig. 2

Fig.2 BMU co-operative education model

As students follow academic courses and work simultaneously, it is beneficial if their work placement is as close as possible to the university. At BMU, students study and work in the same building, as its Business and Education Center in Niš (Fig.3) provides the working space to IT companies that participate in the BMU co-op program.

Fig. 3: Business & Education Center of BMU

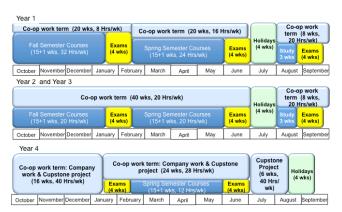

Having the learning curves of students in mind, BMU co-op programs use different workload distribution of students between academic courses and work terms. Fig.4 shows maximum allowed work of students in a company during a four-year bachelor co-op program. Students may work less, if it is agreed with companies, but not more.

Fig. 4: Workload distribution between work and education for coop students.

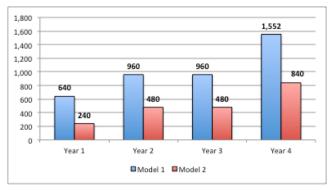

Freshmen students have only 8 hours/week of work in Semester 1 and 16 hours/week in Semester 2. In 2<sup>nd</sup> and 3<sup>rd</sup> year, students may work up to 20 hours/week, and in the 4<sup>th</sup> year they have a full-time work (40 hours/week) in Semester 7 and up to 28 hours/week in Semester 8. The workload distribution of co-op students depends on the company. Table 1 presents two extreme co-op models with a maximum and minimum workload of co-op students during their four years bachelor program. Fig. 5 shows the annual work time of students in case of these two co-op

models. Each company decides about its co-op model. The actual co-op model, in most cases, will have the numbers of work hours of students between these two extremes.

Each company can choose the workload model that suites the company best, but it can be between the two extreme workload models given in Table 1 and Fig. 5. It means that the maximum workload is **24 months** and minimum workload is **12 months** during a period of four years (48 months.)

$\label{eq:table_interpolation} TABLE\ I$  Two models of workload of co-op students

|          | Model No.  | . 1     |            | Model No. 2 |         | -          |

|----------|------------|---------|------------|-------------|---------|------------|

|          | Weekly     | # of    | Total # of | Weekly      | # of    | Total # of |

|          | Workload   | work    | work       | Workload    | work    | work       |

| Sem.     | (Hrs/wk)   | Hrs/wk  | hours      | (Hrs/wk)    | Hrs/wk  | hours      |

| 1        | 8          | 20      | 160        | 8           | 15      | 120        |

| 2        | 16         | 20      | 320        | 8           | 15      | 120        |

| Summer 1 | 20         | 8       | 160        | 0           | 0       | 0          |

| YEAR 1   |            |         | 640        |             |         | 240        |

| 3        | 20         | 20      | 400        | 16          | 15      | 240        |

| 4        | 20         | 20      | 400        | 16          | 15      | 240        |

| Summer 2 | 20         | 8       | 160        | 0           | 0       | 0          |

| YEAR 2   |            |         | 960        |             |         | 480        |

| 5        | 20         | 20      | 400        | 16          | 15      | 240        |

| 6        | 20         | 20      | 400        | 16          | 15      | 240        |

| Summer 3 | 20         | 8       | 160        | 0           | 0       | 0          |

| YEAR 3   |            |         | 960        |             |         | 480        |

| 7        | 40         | 16      | 640        | 40          | 15      | 600        |

| 8        | 28         | 24      | 672        | 16          | 15      | 240        |

| Summer 4 | 40         | 6       | 240        | 0           | 0       | 0          |

| YEAR 4   |            |         | 1.552      |             |         | 840        |

| TOTAL    |            |         | 4.112      |             |         | 2.040      |

| 1        | Total work | months: | 24,48      | Total wor   | k month | 12,14      |

Fig. 5 Maximum and minimum workload of co-op students

BMU co-op partner companies have to provide mentors that work with co-op students and they give them homework and project assignments. Co-op students must submit reports to professors or teaching assistants of each academic course, reporting relevant work they have achieved for each of courses they have in their curriculum.

#### B. Specifics of the BMU Co-op Education Program

BMU does not require that students find companies (as in Canada, for instance) where they can work during the work terms of the co-op program. BMU makes special arrangement with interested companies and connects students with their companies.

As BMU is a private university and students need to pay tuition fees, it is very important for students to have an option of free education, i.e. to avoid paying tuition fees. Having this in mind, BMU requires that its co-op education business partners pay tuition fees for students that will be their scholars. In return, students have to work in the company during their studies throughout four years, according to the workload model specified by the company and they have to work for the company (if the company asks them) at least four years after the graduation.

It is up to the company to decide the value of their scholarship to be given each month to their scholars during their studies.

For each student, the company, the student and BMU make a contract that specifies the mutual obligations and rights of their participation in the BMU co-op program in detail.

#### III. RESPONSIBILITIES OF PARTNERS

Each partner has the following responsibilities and obligations:

#### 1. IT Company:

- a. IT Company offers N scholarships to its scholars (for instance, 30, 85 and 250 EUR/month – for 1<sup>st</sup>, 2<sup>nd</sup> and 3<sup>rd</sup>, and 4<sup>th</sup> year, separately)

- b. IT Company pays tuition fees to BMU: 2.000 EUR per year per student

#### 2. Student:

- a. Partially works for the IT Company and studies

- b. Must acquire 60 ECTS per year with minimum average grade: 8,00

- c. Must work for the IT Company for at least 4 years after graduation.

#### 3. BMU:

- a. Adopts assignments and electives of the scholar to the needs of the IT Company

- b. Provides needed workspace for the IT Company in BEC building in Niš (free 2m² per scholar, the rest is rental)

#### IV. FINANCIAL ASPECTS OF THE COOPERATION

IT companies, not only in Serbia, are facing the problem of lacking of IT engineers and programmers these days. The BMU co-operative education program aims to help solving this problem by:

educating and developing new fresh IT graduates, based on the contract between the university and the future employer,

providing parallel work placement of IT students, for at least 12 months during their four years bachelor program.

IT companies, normally, raise few expected questions:

- Are these students useful and can they really contribute to our business before graduation?

- If we have to pay tuition fees for four years, and scholarships to our scholars, is it a cost-effective investment?

The answer to the first question will be provided in next section of this paper, but the answer to the second question is provided here.

Table II shows the cost of a work-hour of a student that is fully covered with the paid tuition fee (2.000 EUR/year) and the scholarship in case of a maximum workload of students (Model 1) and of a minimum workload (Model 2). The level of scholarships depends on the company. Scholarships used in Table II are assumed levels. They depend on students' workload and having in mind that scholarships are not taxed up to 10.600 Din/month (cca 85 EUR/month).

TABLE II

COST OF STUDENTS' WORK IN CASE OF TWO MODELS OF WORKLOAD

| Model N | Model No. 1 (maximum of student work load) |           |         |           |           |           |  |

|---------|--------------------------------------------|-----------|---------|-----------|-----------|-----------|--|

|         |                                            | Net       | Gross   |           |           |           |  |

|         |                                            | Scholarsh | Scholar | Gross     |           | Cost of   |  |

|         | Total # of                                 | ip        | ship    | Annual    | Annual    | student's |  |

|         | work                                       | (EUR/mo   | (EUR/m  | Scholarsh | Tuition   | work      |  |

|         | (Hours)                                    | nth)      | onth)   | ip (EUR)  | Fee (EUR) | (EUR/hr)  |  |

| YEAR 1  | 640                                        | 30        | 30      | 360       | 2.000     | 3,69      |  |

| YEAR 2  | 960                                        | 85        | 85      | 1.020     | 2.000     | 3,15      |  |

| YEAR 3  | 960                                        | 85        | 85      | 1.020     | 2.000     | 3,15      |  |

| YEAR 4  | 1.552                                      | 250       | 286     | 3.436     | 2.000     | 3,50      |  |

| TOTAL   | 4.112                                      |           |         | 5.836     | 8.000     | 3,36      |  |

|         |                                            |           |         |           |           |           |  |

Model No. 2 (minimum work load)

|          |         | Net      | Gross    |           |           |           |

|----------|---------|----------|----------|-----------|-----------|-----------|

|          | Total   | Scholars | Scholars | Gross     |           | Cost of   |

|          | amount  | hip      | hip      | Annual    | Annual    | student's |

|          | of work | (EUR/m   | (EUR/m   | Scholarsh | Tuition   | work      |

| Semester | (Hours) | onth)    | onth)    | ip (EUR)  | Fee (EUR) | (EUR/hr)  |

| YEAR 1   | 240     | 30       | 30       | 360       | 2.000     | 9,83      |

| YEAR 2   | 480     | 85       | 85       | 1.020     | 2.000     | 6,29      |

| YEAR 3   | 480     | 85       | 85       | 1.020     | 2.000     | 6,29      |

| YEAR 4   | 840     | 250      | 286      | 3.436     | 2.000     | 6,47      |

| TOTAL    | 2.040   |          |          | 5.836     | 8.000     | 6,78      |

| Month    | s: 12   |          |          |           |           |           |

If a company implements the assumed levels of scholarships, in case of the maximum workload of students (Model 1), the average cost of students' work is **3,36 EUR/hour** (both scholarship and tuition fees are included). In case of a minimum workload of students (Model 2), the average cost is **6,78 EUR/month**.

Table III gives a comparisons of these costs with the cost of work of a junior programmer, employed full-time, having an assumed starting net monthly salary of 600 EUR/month Table III shows that the cost of work of

students during their studies (3,36-6,78 EUR/hour) is lower or comparable with the cost of work of a junior programmer (6,42 EUR/month or more). It means the BMU co-op program offers to IT companies a cost-effective investment in the education of their future IT engineers. If a company has projects and work assignments for its scholars, they can pay-off all investment to their education (tuition fees and scholarships). As IT companies charge the work of junior programmers much more than the cost of work of its scholars, it is realistic to expect that the work of its scholars during their studies even creates some profit to the company.

TABLE III

COST OF STUDENTS' WORK IN CASE OF TWO MODELS OF WORKLOAD

| 0001 | COST OF STORESTING WORLD OF TWO MORESTER OF WORLDONE |            |                               |  |  |  |  |

|------|------------------------------------------------------|------------|-------------------------------|--|--|--|--|

|      | Model of Work                                        | Gross Cost |                               |  |  |  |  |

|      | placement with                                       | per Hour   | Assumptions                   |  |  |  |  |

|      | equiv. 1.840 Hrs/yr                                  | (EUR)      |                               |  |  |  |  |

| 1    | Co-op model 1                                        | 3,36       | if student works 1.840 hrs/yr |  |  |  |  |

| 2    | Co-op model 2                                        | 6,78       | if student works 1.840 hrs/yr |  |  |  |  |

| 3    | Junior programer                                     | 6,42       | for nett salary 600 EUR/mnt   |  |  |  |  |

It is fair to mention that in this analysis some cost factors are not included, such as:

- Cost of mentoring of scholars

- Cost of special training courses of scholars

- Cost of learning time of scholars, when they do not work, but learn what they need to know for a task to be assigned to them.

Having the market cost of work of junior programmers in mind, all these cost factors cannot change the general conclusion that the company can earn enough to recover its investment to its scholars, by using them in its projects during their studies. The costs factors given above are usual cost factors that companies have when employing new graduated IT engineers. So, these cost factors are not specific to the co-op program. In case of the co-op program, this cost incurs earlier than normal (when graduated engineers start working for the company).

The cost-effectiveness of a co-op program, that is obviously achievable, is not most important for IT companies. The most important result of the implementation of co-op programs for IT companies is the solution of the problem of recruiting new IT engineers. By implementing the proposed co-op program, a company may employ a group of new graduated IT engineers, its former scholars, each year. These engineers are fully effective from the first working day, as they are familiar with the technology and work standards of the company, as they were involved in its projects in previous four years, during their studies.

#### V. CAN STUDENTS DELIVER WHAT IS EXPECTED?

It is normal to raise this question, when someone has to decide whether to invest in students' education and to include them in some of the company's projects. In order to provide an explicit answer, we will first give some facts related to the curricula of bachelor programs offered to

students at BMU:

- Curricula of programs in Information Technology, Software Engineering, Game Development and Information Systems are fully compliant with the recommendations of IEEE Computer Society, ACM and AIS [12-15].

- Number of lecture hours and tutorials for most important courses are above usual values.

- BMU implements a modern education methodology where a student plays a very active role working on homework and project assignment every week during each semester.

In order to illustrate what a company can expect from its scholars during their work terms, Table IV shows a list of courses of the two most relevant bachelor programs (Software Engineering and Information Technology). They are fully compliant with IEEE and ACM recommendations [11-13].

TABLE IV

COURSES OF SOFTWARE ENGINEERING AND IT BSC PROGRAMS

|     | COURSES OF SOFTWARE ENGINEERING AND IT BSC PROGRAMS |            |                                       |            |  |  |  |

|-----|-----------------------------------------------------|------------|---------------------------------------|------------|--|--|--|

| S   | SOFTWARE ENGINEERING                                | Hrs<br>/wk | INFORMATION TECHNOLOGY                | Hrs/<br>wk |  |  |  |

|     | CS101 Intr. to OO Programming                       | 7          | CS101 Intr. to OO Programming         | 7          |  |  |  |

| 1   | CS220 Computer Architecture                         | 6          | IT101 IT Fundamentals                 | 5          |  |  |  |

| l ' | MA101 Calculus 1                                    | 5          | MA103 Mathematics for IT              | 5          |  |  |  |

|     | NT111 English                                       | 4          | NT111 English                         | 4          |  |  |  |

|     | CS102 Object and Data Abstraction                   | 7          | CS102 Object and Data Abstraction     | 7          |  |  |  |

| 2   | CS323 C/C++ Progr. Language                         | 6          | CS323 C/C++ Progr. Language           | 6          |  |  |  |

| -   | CS115 Discrete Structures                           | 5          | IT210 IT Systems                      | 5          |  |  |  |

|     | NT112 English 2                                     | 4          | NT112 English 2                       | 4          |  |  |  |

|     | CS103 Algorithms and Data Structure                 | 6          | IT331 Computer Netw. & Comm.          | 5          |  |  |  |

| 3   | SE201 Introd. to Software Engineering               | 7          | CS220 Computer Architecture           | 6          |  |  |  |

| ٥   | IT350 Databases                                     | 6          | IT350 Databases                       | 6          |  |  |  |

|     | NT213 English for IT                                | 4          | NT213 English for IT                  | 4          |  |  |  |

|     | SE211 Software Construction                         | 6          | CS225 Operating Systems               | 5          |  |  |  |

| 4   | IT370 Human-Computer Interaction                    | 5          | IT370 Human-Computer Interaction      | 5          |  |  |  |

| 4   | IT255 Web Systems 1                                 | 6          | IT255 Web Systems 1                   | 6          |  |  |  |

|     | MA202 Calculus 2                                    | 5          | CS324 Scripting Languages             | 6          |  |  |  |

|     | SE321 SW Quality, Testing and Maiten.               | 6          | SE201 Intr. to Software Engineering   | 7          |  |  |  |

| 5   | SE311 SW Design and Architecture                    | 6          | IT335 Computer Sys. & Net. Admi.      | 5          |  |  |  |

| ٦   | SE322 Software Requirements                         | 5          | Elective Course 1                     |            |  |  |  |

|     | IT355 Web Systems 2                                 | 6          | IT355 Web Systems 2                   | 6          |  |  |  |

|     | SE325 Project Mgmnt for SW Devel.                   | 6          | SE325 Project Mgmnt for SW Devel.     | 6          |  |  |  |

| 6   | CS225 Operating Systems                             | 5          | IT333 Wireless and Mobile Comm.       | 5          |  |  |  |

| ١٥  | Elective Course 1                                   |            | IT381 Inform. Security and Safety     | 6          |  |  |  |

|     | Elective Course 2                                   |            | CS330 Development of Mobile Appl.     | 6          |  |  |  |

|     | Co-op Program (4 months,8 hrs/day)                  | 40         | Co-op program (4 months,8 hrs/day     | 40         |  |  |  |

| 7   | Elective Course 3 (online)                          | 6          | Elective Course 2 (online)            |            |  |  |  |

| ľ   | IT390 Prof. Practice & Etics (online)               | 5          | IT390 Prof. practice & Etics (online) | 5          |  |  |  |

|     | NT310 Prof. Communications (online)                 | 5          | NT310 Prof. Communications (onl.)     | 5          |  |  |  |

|     | IT381 Information Security and Safety               | 6          | Elective Course 3                     |            |  |  |  |

| 8   | Elective Course 4                                   |            | Elective Course 4                     |            |  |  |  |

|     | SE495 Cupstone Project                              |            | IT495 Cupstone Project                |            |  |  |  |

|     | ELECTIVE COURSES                                    |            | ELECTIVE COURSES                      |            |  |  |  |

| 6   | CS324 Scripting Languages                           | 6          | MA273 Probability and Statistics      | 5          |  |  |  |

| 6   | MA273 Probability and Statistics                    | 5          | IS250 Arch of Enterprise IT Systems   | 6          |  |  |  |

| 6   | CS330 Development of Mobile Appl.                   | 6          | CS322 Programming in C#               | 6          |  |  |  |

| 6   | IT333 Wireless and Mobile Comm.                     | 5          | IS310 Enterprise IS                   | 5          |  |  |  |

| 7   | IT320 Adv. Technology Platforms                     | 6          | IT320 Adv. Technology Platforms       | 6          |  |  |  |

| 7   | IS345 Management of Digital Content                 | 6          | IS345 Manag. of Digital Content       | 6          |  |  |  |

| 7   | IT331 Computer Netw. & Comm.                        | 5          | OM350 Enterpreneourship               | 6          |  |  |  |

| 7   | CS322 Programming in C#                             | 6          | IS330 IS Strategy and Management      | O          |  |  |  |

| 8   | SE401 SW Development Project                        | 5          |                                       |            |  |  |  |

| 8   | OM350 Enterpreneourship                             | 6          |                                       |            |  |  |  |

After the first year, students should be able to perform simple programming tasks in Java and C++, as they had three programming courses in first two semesters:

- CS101 Introduction to OO programming (7 hrs. /wk.)

- CS102 Object and Data Abstraction (7 hrs. /wk.)

- CS323 C/C++ Programming Language (6 hrs. /wk.)

For each course, students get homework assignments each week and have to realize a project, by developing an application in Java and in C++.

After the second year, Software Engineering students should be able to perform tasks of junior Java or C++ programmers, as they have the following courses:

- CS103 Algorithms and Data Structure (6 hrs. /wk.)

- SE201 Introduction to Software Engineering (7 hrs. /wk.)

- IT350 Databases (6 hrs. /wk.)

- SE211 Software Construction (6 hrs. /wk.)

- IT370 Human-Computer Interaction (5 hrs. /wk.)

- IT255 Web Systems (6 hrs. /wk.)

After completing the Year 3, students are ready for software development projects, as they had all needed software engineering courses:

- SE321 SW Quality, Testing and Maintenance

- SE311 Software Design and Architecture

- SE322 Software Requirements

- SE325 Project Management for SW Development

- Web front-end programing (Web Systems 1) and web back-end programming (Web Systems 2). Besides CS225 Operating Systems, they also have two elective courses in Semester 6.

They have full-time (40 hrs. /wk.) working term in a company, i.e. BMU co-op partner during Semester 7. Besides studying two courses (IT381 Information Security and Safety and a elective course) the main activity in Semester 8 is the SE495 Capstone project. If a student is the scholar of a BMU co-op partner, it is expected that its future employer, BMU co-op partner, would specify its capstone project.

Having the curricula of Software Engineering, Information Technology, Game Development and Information Systems bachelor programs at BMU [11-15] in mind, we are sure that students may perform many programming tasks during their work terms in companies, BMU co-op partners.

#### VI. THE LEARNING MODEL OF BMU CO-OP

The co-op education includes school-based and work-based learning. When implementing a parallel co-op model, like the BMU co-op model, it is necessary to split the students daily activities between academic courses and work in their companies. Actually, their work should be structured according to their class schedule.

When students follow a traditional, in-class academic program they have at least 20 contact (active) hours a week, or four in-class hours per working day. If the

company does not operate in the same location or near the university, due to travel time of students between the university and company, the available working time, in daily basis is limited to maximum three, in average. One solution of the problem is to schedule courses is such a way that students have two days a week free for their work in companies, and three days when they have courses, with cca seven in-class hours a day, in average. This structuring model of students' activities restricts companies to use students only two days a week. This interruption of their work may disturb their work in company projects, because they normally work in teams with others fully employed team members. If they are completely out of work three days a week, these projects may be seriously affected

An alterative to traditional (in-class) mode of learning is to implement online mode of learning. In this case, co-op students would share their time between their work placement in companies and study activities at home. In this case, co-op students and companies can more easily coordinate their work and learning time. This solution is definitely better for companies, but students have to be highly motivated and well self-organized to successfully realize their on-line courses and learning at home.

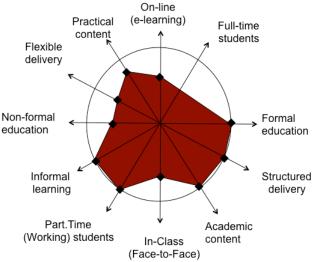

BMU co-op model is offering a more appropriate mode of learning, a hybrid or blended learning. Students need to read and learn the content of online lessons, delivered by the e-learning system of BMU at home and come to the university for in-class tutorials and lab work. In this scheduling model, students spend less time at university in classes, in comparison with traditional mode of studying, but still use the benefits of direct communication with their lecturers and teaching assistants during tutorials and lab works. This is a compromise solution that combines good features of all three modes of learning:

- On-line learning using provided learning content gives students an opportunity to learn when they are ready for this, and they also learn how to learn alone, which they will need to do during their professional life any way.

- *In-class tutorials and lab work* provide very useful interactions of a student with other students and with lecturers and teaching assistants. This can help them to better acquire new knowledge and skills.

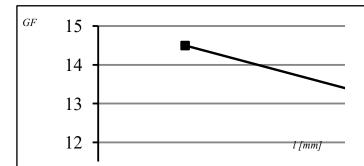

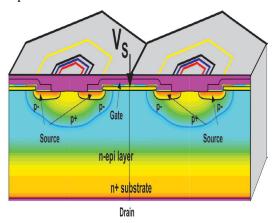

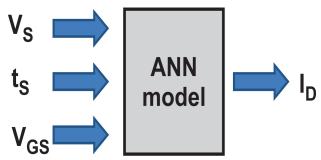

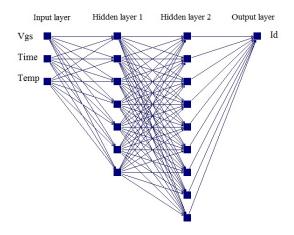

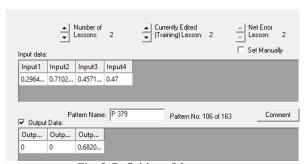

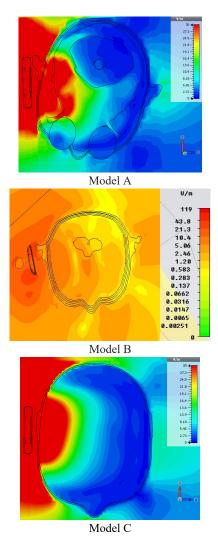

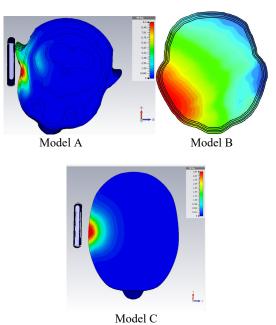

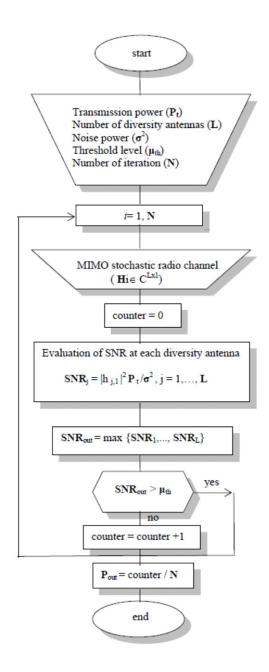

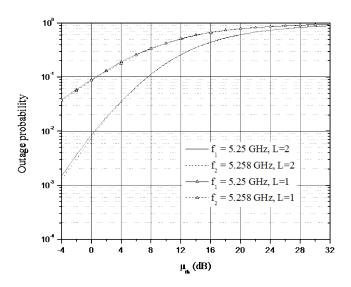

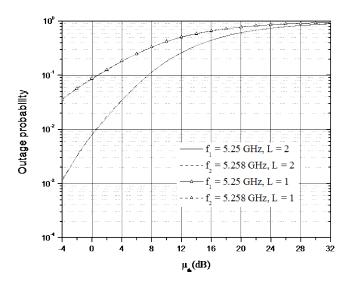

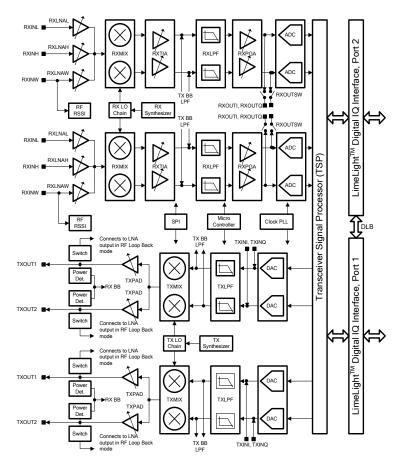

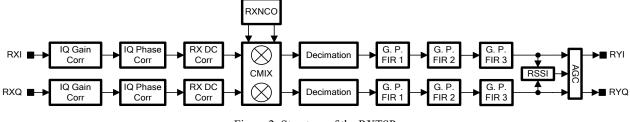

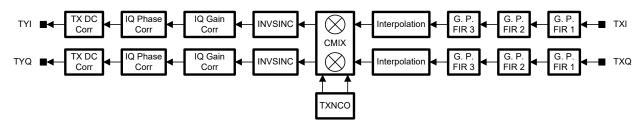

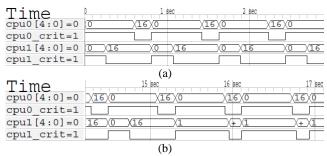

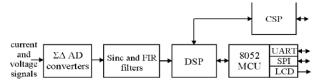

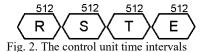

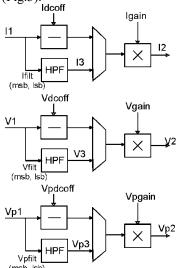

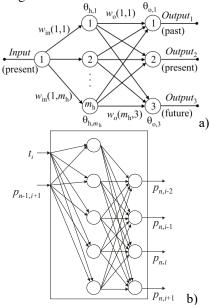

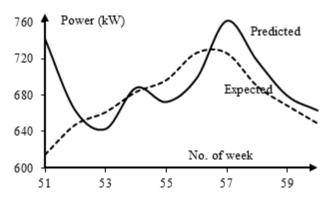

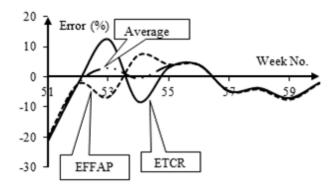

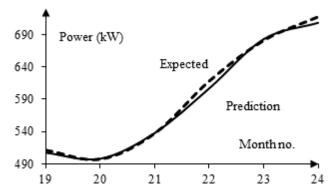

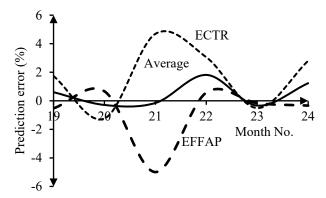

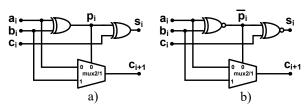

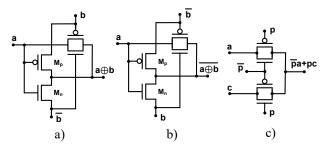

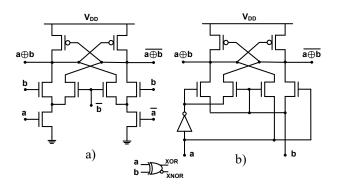

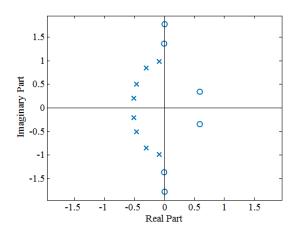

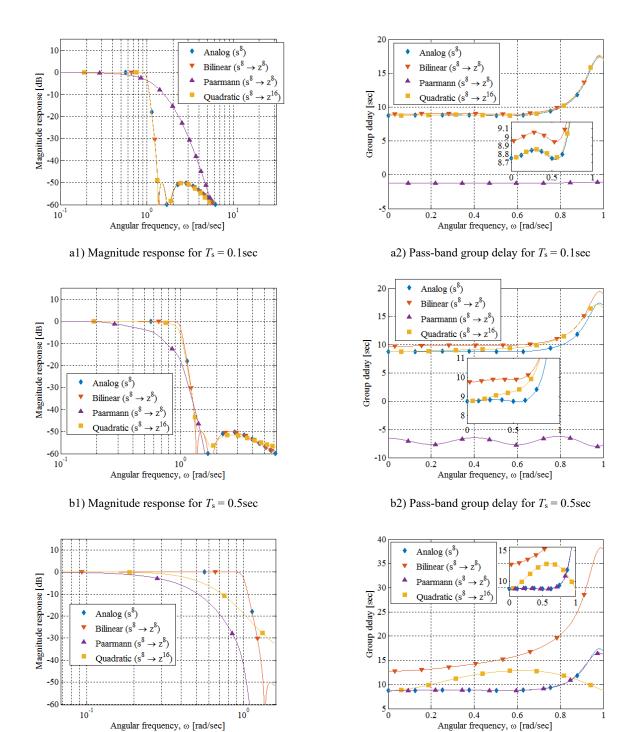

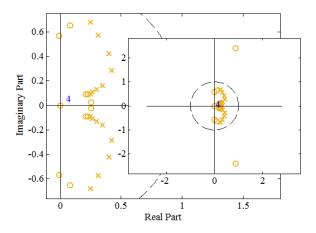

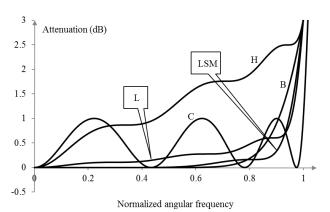

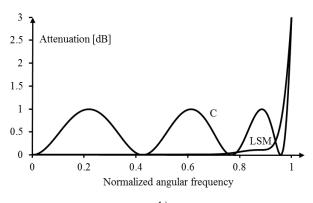

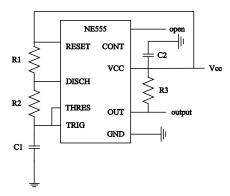

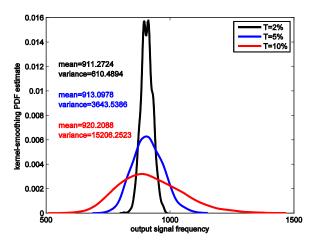

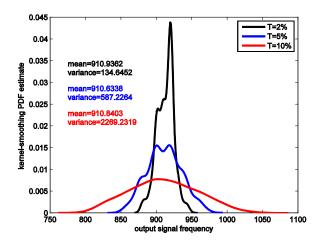

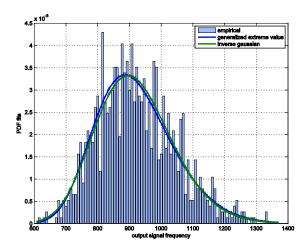

- Informal learning during their work in a company, helps a co-op student to learn something that is not normally offered in academic courses, such as technologies and working practices that are specific to the company their future employer.